線上影音

Home > ANSYS SIwave教學> 定義目標阻抗的電源完整性優化設計

本文始於2019年,探討電源完整性優化設計流程,與採用不同目標阻抗(target impedance)定義的差異。

![]()

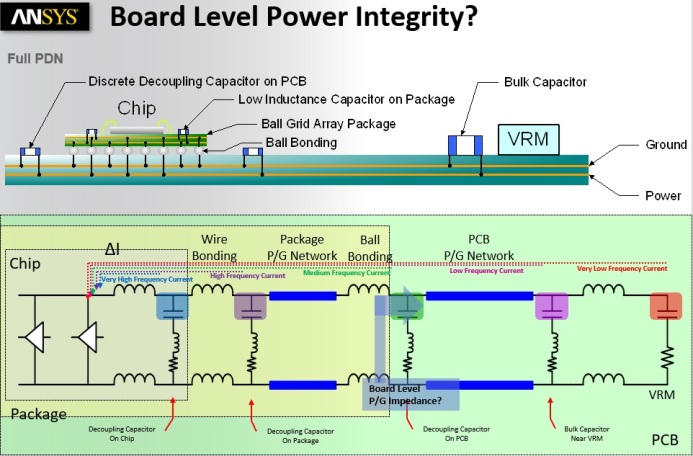

從VRM(Voltage Regulator Module)到IC端整個電源網路PDN(Power Delivery/Distribution Network),其實有區分PCB板級/封裝級/IC級,越接近IC端,去耦合電容所能影響(改善)的頻段越高。

一般板級的去耦合電容,有效的作用頻段約在60~80MHz以下,百MHz級的頻段必須靠封裝端的去耦合電容,數百MHz級的頻段則要靠IC內的電容。

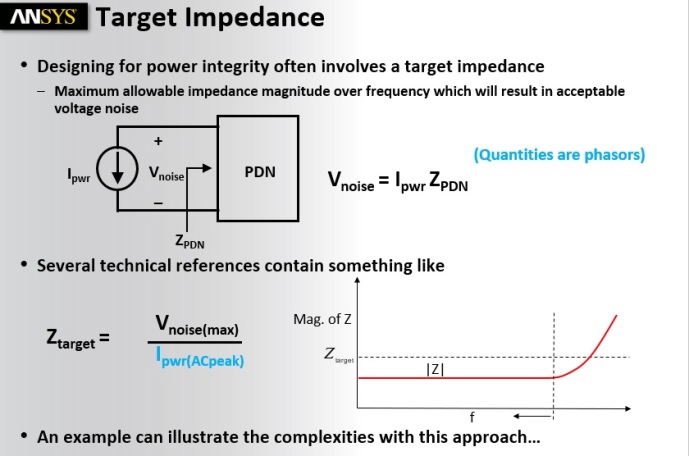

在電源完整性優化設計的流程中,如何定義目標阻抗是一個很重要的議題,且目標阻抗值是可以隨頻率不同的。[7]

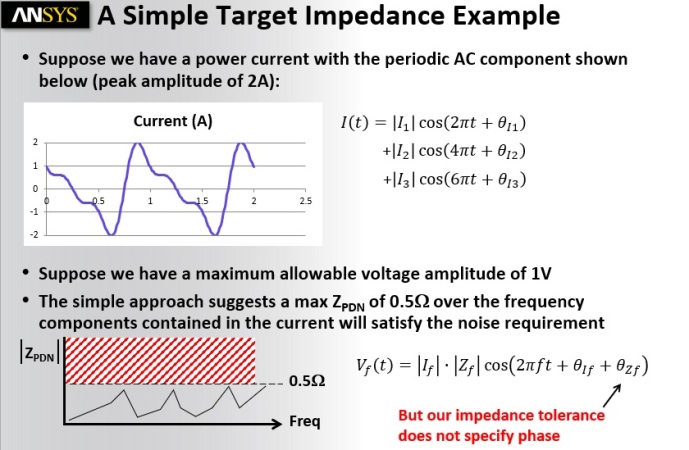

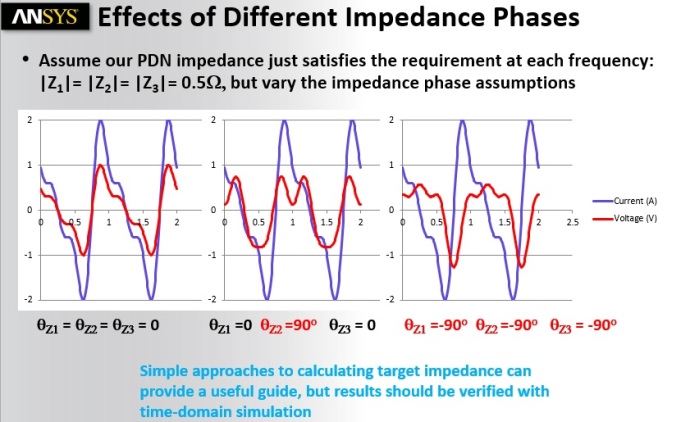

假設最大電流2A,可容許最大電壓波動1V,則最大容許阻抗建議值0.5歐姆。而這依歐姆定律簡單得到的阻抗值,只有考慮電壓/電流大小,沒有考慮相位關係。

如果把量測或模擬得到的電流時域波形,透過FFT轉換後拿來除最大允許電壓波動值,得到隨頻率變化的阻抗曲線當目標阻抗,以此做為Z11的優化依據,所得到的電壓時域波形並無法滿足最大電壓波動規格的範圍。主要原因是,沒有考慮相位相對的關係。也就是頻域上不同頻點的電流能量,在時域上可能是同相位的,若以R(f)=Vripple/I(f)得到目標阻抗,此時是把每個頻點的電流能量分開考慮的,無法考慮到時域上不同頻率成分會因為同相位導致電流震幅會累加,也就是過於寬鬆的設計標準。

以上透過相位來解釋如果還是不懂,換個大白話方式說:假設時域上某個電流振幅最大的峰值Ipp(Imax),該電流I(t)從時域轉到頻域的成份絕對不會是頻域上單一根頻點的能量所構成(除非該Ipp是正弦波), 而是在頻譜上多根頻率的能量所合成,所以把I(t)轉成I(f),後者是沒辦法反映Imax的強度的。故直接以V/I(f)當target impedance limited line會是一個過鬆的標準(無法滿足設計需求)。

但若把電壓直接除以Imax的阻抗當全頻帶(0~1GHz)優化目標,這樣又會over design(過嚴苛標準)。

折衷方式是,先在頻域針對不同頻段的Z11進行優化,再以時域波形來檢驗是否需要進一步改善,也就是分頻域與時域兩階段疊代進行設計優化。

4.1 使用Imax-Imin得到目標阻抗 [5]

4.2 使用0.5*Imax得到目標阻抗 [6][7]

- 案例實測

5.1 優化前PDN的Z11 profile

PDN優化前在IC端掛上電流負載時Ipp=0.45A,此時所看到的電壓波動Vpp=4.42V, Vavg=3.3V

5.2 採用步驟4.2中所介紹的目標阻抗選擇原則:

Vripple=3.3*(±10%)=±0.33V, Imax=Ipp=0.45A, Rmax=Vripple/(0.5*Imax)=1.466 ohm

步驟4.2投影片中,畫出而沒說出的重點在0~1GHz以內把Z11壓在Rmax以下,1G以上可以容許略為超出。

果然電壓波動幅度可以滿足小於±10%的目標

1GHz以上的Z11特性,難道完全不用在意嗎? 當然不是!

下圖是Ldie從0.01nH~0.09nH變化,整個Z11與時域電壓波形變化的趨勢,我們可以很清楚的看出,1GHz以上Z11超出也是會導致電壓波形波動範圍超標的。

那1GHz以上的目標阻抗該如何定呢?

如果Lpkg沒法做到0.3nH,Cpkg客戶也不容許加0.68nF,那怎麼進一步優化?

我們繼續看下去 ...

5.3 使用電流FFT轉換後的倍數為基礎,訂出0~10G的動態目標阻抗

如果直接以Vripple/FFT(I),這樣得到的目標阻抗並不具實用性(過鬆的標準)

但如果以Vripple/[n*FFT(I)]而取n=30得到的目標阻抗做電源完整性優化,在此例上效果很好

也就是靠調整n , 讓下降後的藍線Vripple/[n*FFT(I)], 其低頻部分(0~10M)的平均降到可貼近Vripple/(0.5*Imax)=1.466準位的程度

- 問題討論

優化(加強)PCB板級設計,放寬封裝級設計,同樣滿足最終Vripple<±10%規格(0.66V)。至此, 本文要闡述的重點出現了:

在VRM->PCB板->封裝->IC這一串電源傳遞路徑上,電源完整性優化的對策下在哪一層級上最有效、最低成本,常是IC、封裝、PCB板設計部門彼此間花很多時間討論(或爭論)的焦點,透過本文所介紹的手法,可以讓大家早期預估,針對您設計上最具挑戰的頻段,採取最適合的有效對策。

[1] Chulsoon Hwang, "Power Integrity Concepts for High-Speed Design on MultiLayer PCBs", IEEE Symposium on EMC, SI & PI, workshop and tutorials, 2018.

[2] K. Shringarpure, S. Pan, "Innovative PDN Design Guidelines for Practical High Layer-Count PCBs", DesignCon2013.

[3] Tzong-Lin Wu, "Power Integrity and EMC Design for High High-speed Circuits Packages", IEEE Symposium on EMC, workshops and tutorials, 2008.

[4] Greg Pitner, Isaac Waldron, "Chip-Aware Power Integrity", ANSYS UGM 2012.

[5] Larry Smith, Eric Bogatin, "Principles of Power Integrity for PDN Design", IEEE Symposium on EMC, SI & PI, workshop and tutorials, 2018.

[6] Zhiping Yang (Google Inc.), "Fundamentals of Power Integrity", IEEE Symposium on EMC, SI & PI, workshop and tutorials, p.23, 2018.

[7] 台大吳瑞北教授, "Power Integrity in SiP"課程, Lecture2:Fundamental, p51,53

[8] F De Paulis, B Zhao, S Piersanti, "Impact of Chip and Interposer PDN to Eye Diagram in High Speed Channels", 2018 IEEE 22nd Workshop on Signal and Power Integrity (SPI).

[9] On-Die Power Integrity Measurements, Eric Bogatin

[10] Larry Smith, Eric Bogatin, papers